本文转自电子工程世界(EEWorld)。

在下周的VLSI会议上,英特尔将发布两篇论文,介绍即将推出的PowerVia芯片制造技术的进展。而在第三篇论文中,英特尔技术专家Mauro Kobrinsky还将阐述英特尔对PowerVia更先进部署方法的研究成果,如同时在晶圆正面和背面实现信号传输和供电。

PowerVia将于2024年上半年在Intel 20A制程节点上推出。

作为延续摩尔定律的关键技术,英特尔将PowerVia技术和RibbonFET晶体管的研发分开进行,以确保PowerVia可以被妥善地用于Intel 20A和Intel 18A制程芯片的生产中。在与同样将与Intel 20A制程节点一同推出的RibbonFET晶体管集成之前,PowerVia在其内部测试节点上进行了测试,以不断调试并确保其功能良好。经在测试芯片上采用并测试PowerVia,英特尔证实了这项技术确实能显著提高芯片的使用效率,单元利用率(cell utilization)超过90%,并有助于实现晶体管的大幅微缩,让芯片设计公司能够提升产品性能和能效。

PowerVia 和 RibbonFET的组合,尤其是PowerVia被英特尔视为新的“FinFET”时刻,毕竟在RibbonFET上,和其他对手的GAAFET相比不会领先,但PowerVia是绝对领先的。预计台积电在2026年底或2027年初的N2P节点之前不会部署这项技术。

也正因此,PowerVia被英特尔拿来与如应变硅(strained silicon)、高K金属栅极(Hi-K metal gate)和FinFET晶体管的创新相提并论,这几项技术都是英特尔率先在业界推出的。

“这是英特尔迎接埃米(angstrom)时代的创举”,更重要的是Intel 20A和Intel 18A制程不只是面向英特尔产品,同时也对英特尔代工服务(IFS)具有深远意义。

英特尔的PowerVia是什么

英特尔提供过一段视频,以形象的介绍PowerVia架构,具体可参考https://www.intel.com/content/www/us/en/silicon-innovations/6-pillars/process.html。

背面供电网络 (BSP/BS-PDN) 是过去几年在整个芯片制造行业悄然发展的技术,与EUV类似,BS-PDN也被视为继续开发更精细工艺节点技术的基石。

想了解背面供电网络的价值,就需要从芯片制造开始了解。芯片内部的功率传输网络需要从蚀刻晶体管的第一层开始,这是芯片上最小和最复杂的层,也是最需要EUV和多重曝光等高精度工具的地方。简而言之,它是芯片中最昂贵和最复杂的层,对芯片的构造方式和测试方式都有重大影响。

在此之上,逐渐搭建各种金属层,以将电子传输到不同晶体管(包括缓存、缓冲器、加速器)之间所需的所有布线,并进一步为更上层的电源提供路由。 英特尔将这比喻成制作比萨饼,这是一个粗略但形象的比喻。

现代高性能处理器通常有10到20个金属层。比如Intel 4工艺,有16个逻辑层,间距从 30 nm到280 nm。 然后在其之上还有另外两个“巨型金属”层,仅用于电源布线和放置外部接口。

芯片制造完成之后,就会被翻转过来倒装,然后所有的连接部分,包括电源和数据接口就变到了芯片底部,晶体管在芯片顶部。倒装的好处是芯片调试和冷却可以从顶部接触,从而变得更为方便。

然而,前端供电的缺点在于,电源线和信号线都位于芯片的同一侧。两条线都必须向下穿15层以上才能到达晶体管,既要争夺空间,同时还要避免干扰,并且距离越长,电阻越大,效率越低,这被称为IR Drop/Droop效应。

在芯片制造的大部分历史中,这并不是一个大问题。但随着芯片尺寸越来越小,这一问题开始凸显。前端功率传输没有明显的硬性限制,但考虑到每一代芯片都越来越难缩小,这个问题已经变得太大(或者更确切地说太昂贵)而无法解决。

背面供电则是将信号和电源传输网络分开,一侧是信号,另外的一侧(背面)是电源。

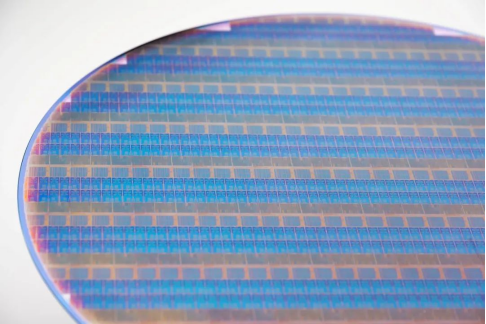

对于Intel的PowerVia实施这一概念,Intel实际上是将晶圆倒置,并抛光几乎所有剩余的硅,直到它们到达晶体管层的底部。 届时,英特尔随后会在芯片的另一侧构建用于供电的金属层,类似于他们之前在芯片正面构建它们的方式。最终结果是,英特尔最终得到了本质上是双面芯片,一侧传输电源轨,另一侧传输信号。

PowerVia的好处

迁移到背面供电有许多好处,首先,这对简化芯片的构造具有重要影响。可以放宽金属层的厚度,Intel 4 + PowerVia的测试节点允许36 nm间距,而不是在Intel 4上要求30 nm间距。

背面供电网络也准备好为芯片提供一些适度的性能改进。通过更直接的方式缩短晶体管的功率传输路径有助于抵消IR Droop效应,从而更好地向晶体管层传输功率,并且消除干扰,英特尔称之为“解决了数十年来的互连瓶颈问题”。

PowerVia的难点

首先是测试难题,晶体管层现在大致位于芯片的中间,而不是末端。这意味着传统的调试工具无法直接戳穿已完成的芯片的晶体管层进行测试,而现在晶体管层和散热层之间有 15 层左右的信号线。这些并非无法克服的挑战,正如英特尔的论文所仔细阐述的那样,而是英特尔在其设计中必须解决的问题。有趣的是,英特尔甚至在芯片设计中放置了一些“复活节彩蛋”缺陷,以便为英特尔的验证团队提供一些半可控的缺陷。据英特尔称,他们的验证团队使用他们的PowerVia调试工具发现了所有这些Bug,有助于证明这些调试过程的有效性。

其次是制造难题,在芯片背面构建电源层是以前从未做过的事情,这增加了出错的可能性。 因此,不仅电力传输需要工作,而且还不能影响良率。

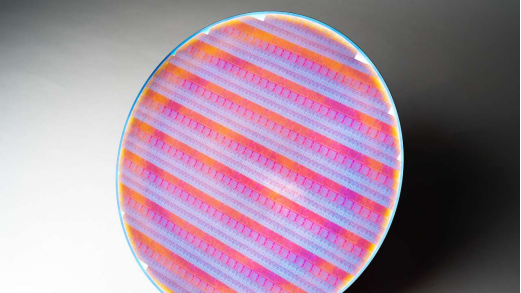

英特尔使用了载体晶圆(carrier wafer)作为其构建过程的一部分,以提供芯片刚性。 在 PowerVia 晶圆的正面制造完成后,载体晶圆被粘合到该晶圆的正面,它是一个虚拟晶圆,以帮助支撑芯片。由于双面芯片制造工艺会磨掉太多剩余的硅晶圆,因此没有多少结构硅可以将整个芯片结合在一起。

反过来,该载体晶圆在其余下的生命周期中仍然是芯片的一部分。一旦芯片制造完成,英特尔就可以将键合的载体晶圆抛光到所需的厚度。 值得注意的是,由于载体晶圆位于芯片的信号侧,这意味着它在晶体管和冷却器之间存在另一层材料。英特尔改善热传递的技术已经考虑到了这一点。

特别的,英特尔还使用 TSV 进行电源布线。在PowerVia中,芯片的晶体管层中有纳米级 TSV(恰如其分地命名为 Nano TSV)。虽然电源轨仍然需要向上和越过晶体管层来输送电力,但使用 TSV 可以让电力更直接地输送到晶体管层,避免了必须设计和内置埋入电源轨所需的路由。

“Blue Sky Creek”证明了PowerVia的成功

相比RibbonFET,PowerVia的风险更高。因此,英特尔将两项技术分别研发,并为 PowerVia 开发一个临时测试节点。即便PowerVia开发没有如期完成,英特尔仍然可以推出不含PowerVia的RibbonFET产品。

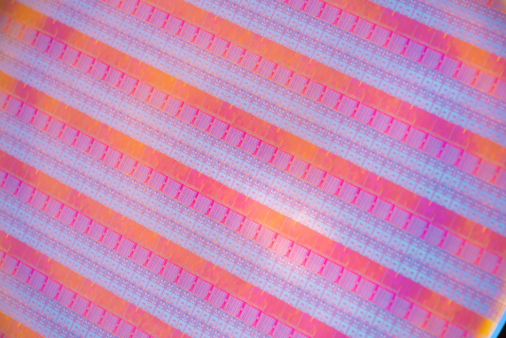

研发代号为“Blue Sky Creek”的测试芯片,就是PowerVia与Intel 4的结合。

Blue Sky Creek源自Intel的Meteor Lake平台,使用两个基于Intel Crestmont CPU架构的E-cores die。Intel 在这里使用Crestmont的原因有两个:首先,它最初是为Intel 4设计的,使其成为移植到Intel 4 + PowerVia工艺的一个很好的候选者。其次,因为E-cores很小; 四核测试裸片的尺寸仅为33.2平方毫米(4毫米x 8.3毫米),这使得它们在测试复杂性和不必在实验工艺节点上实际生产大型裸片之间取得了良好的平衡。

PowerVia的测试也利用了极紫外光刻技术(EUV)带来的设计规则。在测试结果中,芯片大部分区域的标准单元利用率都超过90%,同时单元密度也大幅增加,可望降低成本。测试还显示,PowerVia将平台电压(platform voltage)降低了30%,并实现了6%的频率增益(frequency benefit)。PowerVia测试芯片也展示了良好的散热特性,符合逻辑微缩预期将实现的更高功率密度。

英特尔技术开发副总裁Ben Sell表示:“英特尔正在积极推进‘四年五个制程节点’计划,并致力于在2030年实现在单个封装中集成一万亿个晶体管,PowerVia对这两大目标而言都是重要里程碑。通过采用已试验性生产的制程节点及其测试芯片,英特尔降低了将背面供电用于先进制程节点的风险,使得我们能领先竞争对手一个制程节点,将背面供电技术推向市场。”

关键词:

首页

首页

营业执照公示信息

营业执照公示信息